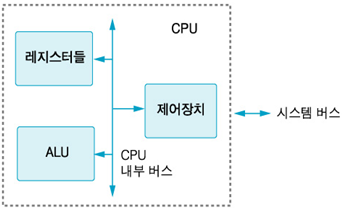

중앙처리장치(CPU)란? 중앙처리장치(CPU)는 명령어의 해석과 자료의 연산, 비교등의 처리를 제어하는 컴퓨터 시스템의 핵심장치이다. 다양한 입력 장치로부터 정보를 입력받아 처리한 후, 그 결과를 출력장치로 보내는 일련의 과정을 제어하고 조정하는 일을 수행한다. CPU는 사람의 두뇌와 같이 컴퓨터의 모든 시스템을 제어, 처리하는 가장 핵심적인 장치라고 할 수 있다. CPU의 구성요소 CPU는 크게 제어 장치, 연산 장치(ALU), 레지스터 와 각 구성 요소를 연결하는 내부 버스로 구성되어 있다. 1. 제어 장치 (CU, Control Unit) 컴퓨터 시스템의 작동을 통제하고 지시하는 장치 기억 장치로부터 프로그랭 명령을 순차적으로 꺼내 해독하고, 해석에 따라서 명령어 실행에 필요한 제어 신호를 기억장치..